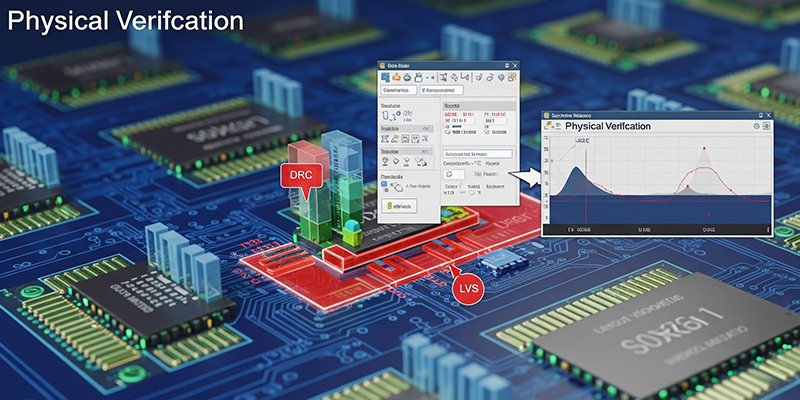

Signoff-Quality Physical Verification

Sanketh Semiconductors provides comprehensive physical verification services ensuring your design meets all foundry requirements for manufacturability. Our team specializes in DRC (Design Rule Checking), LVS (Layout vs Schematic), ERC (Electrical Rule Checking), and ANT (Antenna Rule Checking) using industry-standard tools like Calibre, IC Validator, and Pegasus for nodes from 28nm down to 5nm.

With 120+ successful tapeouts, we've developed optimized physical verification flows that reduce turnaround time by 30% while maintaining 100% accuracy. Our engineers work closely with foundry partners to implement the latest design rules and technology files, ensuring your design passes all checks before tapeout.

Our Physical Verification Flow

Complete verification methodology for signoff confidence:

- Foundry rule deck customization and validation

- Hierarchical DRC/LVS verification

- ERC and antenna checks

- DFM (Design for Manufacturability) analysis

- PERC (Programmable Electrical Rule Checking)

- Metal density and CMP checks

Advanced Capabilities

Our physical verification services include:

- Multi-corner multi-mode (MCMM) verification

- Low-power design verification (UPF-aware LVS)

- 3D-IC and advanced packaging verification

- Custom deck development for unique requirements

- Automated error debugging and waiver management

Why Choose Our Services?

- 40% faster turnaround than industry average

- 100% clean signoff for all tapeouts

- Foundry-certified verification engineers

- 24/7 verification support during tapeout crunch

- Seamless integration with physical design teams

We go beyond basic DRC/LVS to provide manufacturability analysis that improves yield and reduces silicon respins. Our physical verification experts work as an extension of your team, providing actionable feedback to quickly resolve violations and meet aggressive tapeout schedules.