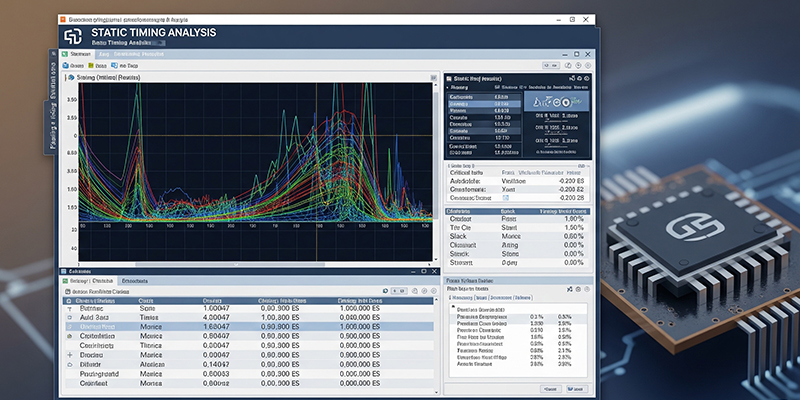

Signoff-Quality Static Timing Analysis

Sanketh Semiconductors provides comprehensive STA services to ensure timing closure for your most complex SoC designs. Our certified timing engineers use industry-leading tools (PrimeTime, Tempus) to analyze and optimize designs from 28nm down to 7nm process nodes, delivering silicon-accurate results.

We specialize in advanced timing analysis including OCV/AOCV/POCV margining, cross-talk delay, and noise analysis. Our team has successfully closed timing for high-performance computing, automotive, and 5G designs with clock frequencies exceeding 3GHz.

Our STA Methodology

Our proven approach to timing closure ensures first-pass silicon success:

- Multi-mode multi-corner (MMMC) analysis with 100+ scenarios

- Advanced OCV/AOCV/POCV margining techniques

- Clock domain crossing (CDC) verification

- Low-power aware timing analysis with voltage scaling

- ECO implementation for final timing closure

- Silicon-correlated timing models

Key Differentiators

What sets our STA services apart:

- Experience with 50+ tapeouts at 7nm/5nm nodes

- Automotive-grade timing closure meeting ISO 26262

- High-speed interface expertise (DDR5, PCIe5, HBM)

- Machine learning-based timing optimization

- Foundry-certified signoff methodologies

Our team has successfully closed timing for designs with over 500M gates and 100+ clock domains. We combine deep technical expertise with rigorous quality processes to deliver predictable, repeatable timing closure.

STA Tool Expertise

We're certified experts in all major STA platforms:

- Synopsys PrimeTime

- Cadence Tempus

- Siemens EDA (formerly Mentor) Nitro-SoC

- Ansys RedHawk-SC

- Apache Totem

- Custom analysis scripts