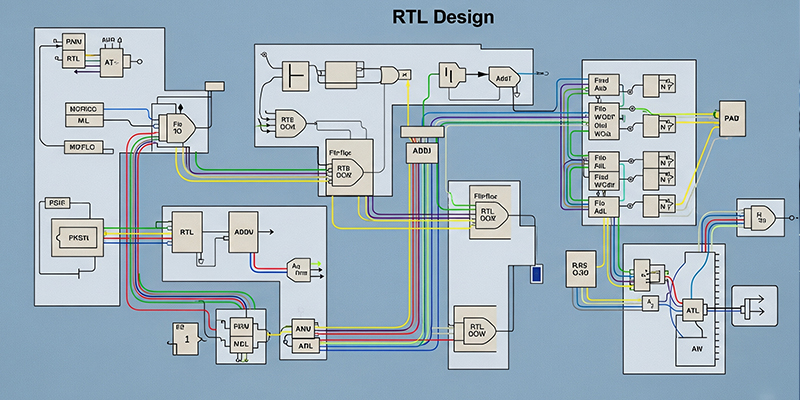

High-Performance RTL Design Solutions

Sanketh Semiconductors provides expert RTL design services for complex ASICs and SoCs, delivering optimized Register Transfer Level implementations that meet stringent power, performance, and area requirements. Our team of 150+ RTL design engineers specializes in creating synthesizable, verification-ready RTL code for applications ranging from AI accelerators to automotive controllers.

We follow strict coding guidelines (based on Reuse Methodology Manual) and employ advanced techniques like power-aware RTL design, clock domain crossing management, and microarchitecture optimization. Our designs have been successfully implemented in 7nm/5nm FinFET technologies for leading semiconductor companies, achieving first-time-right silicon in 90% of projects.

Our RTL Design Methodology

Comprehensive approach ensuring quality results:

- Microarchitecture specification development

- Power-optimized RTL coding (with UPF support)

- Linting and CDC/RDC analysis

- Clock domain crossing verification

- Formal property checking

- Seamless handoff to verification teams

Technical Capabilities

Our RTL design expertise includes:

- High-speed interface design (DDR5/PCIe6/USB4)

- AI/ML accelerator architectures

- Automotive-grade designs (ISO 26262 compliant)

- Low-power design techniques

- Security features implementation

Why Our RTL Design Services?

- 20+ years of collective RTL design experience

- 95% of designs pass synthesis on first attempt

- Verification-ready code with built-in debug hooks

- Seamless integration with our verification services

- Documented design intent and assumptions

We provide complete RTL design solutions from concept to tapeout-ready implementation, including specification development, microarchitecture optimization, and power/performance trade-off analysis. Our designs are optimized for your target technology node while maintaining maximum flexibility for future enhancements.